OHIO SCIENTIFIC INSTRUMENTS

11679 HAYDEN STREET, HIRAM, OHIO 44234

#### THEORY OF OPERATION:

#### Introduction:

The OSI Model 450 is a 400 series PROM board. It used AMI S6834 PROMS (512  $\times$  8) to provide up to 8K bytes per board. An important feature is the on-board PROM programmer which, together with the driver routines in this manual, allows the user to program his own PROMs.

The board is comprised of four subsystems: addressing and data buffering, PROM operation (read only), PROM programmer, and PIA port.

Addressing and Data Buffering:

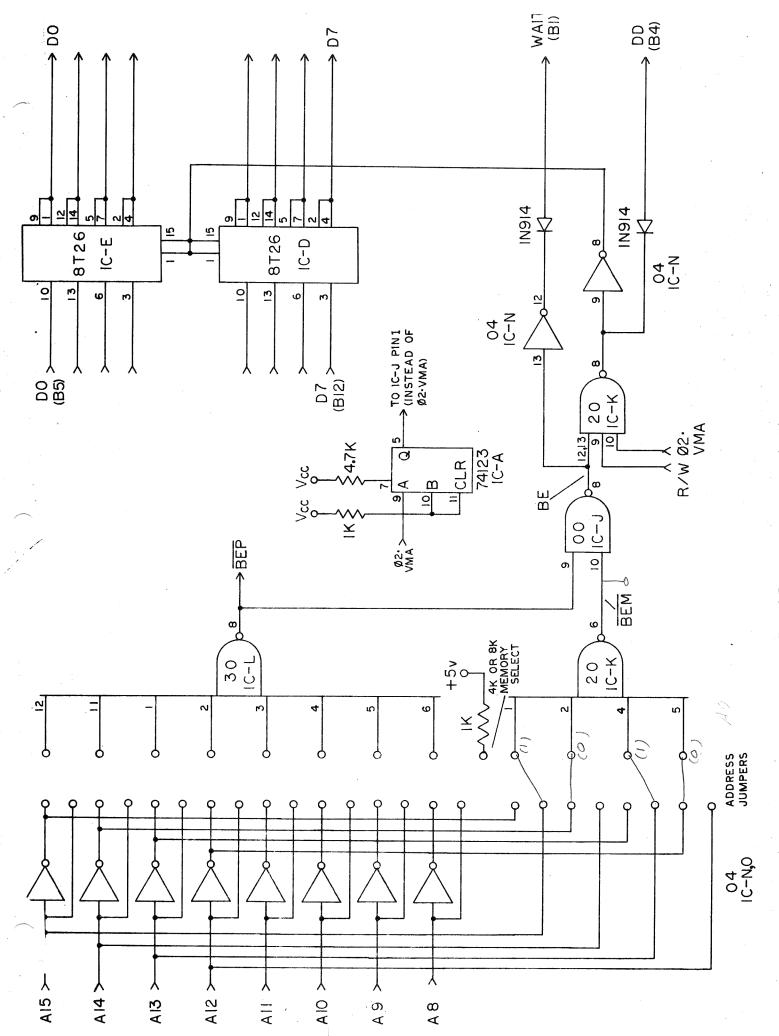

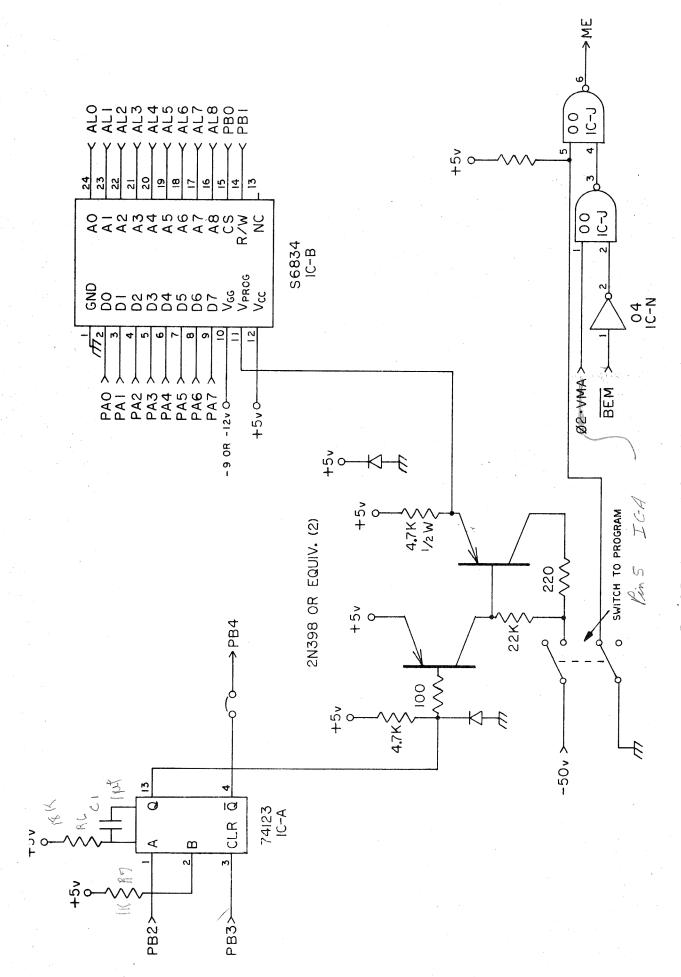

The PROMs and PROM programmer are two separate systems occupying different locations in memory space, hence each has its own address decoder. (See Diagram 1). A programmer enable signal  $\overline{\text{BEP}}$  is derived by NANDing Ag-A<sub>15</sub>. These address lines are present in both inverted and non-inverted forms in the address jumper area in the lower right corner of the board. Normally this should be jumpered for FØXX to be compatible with OSI programming software.

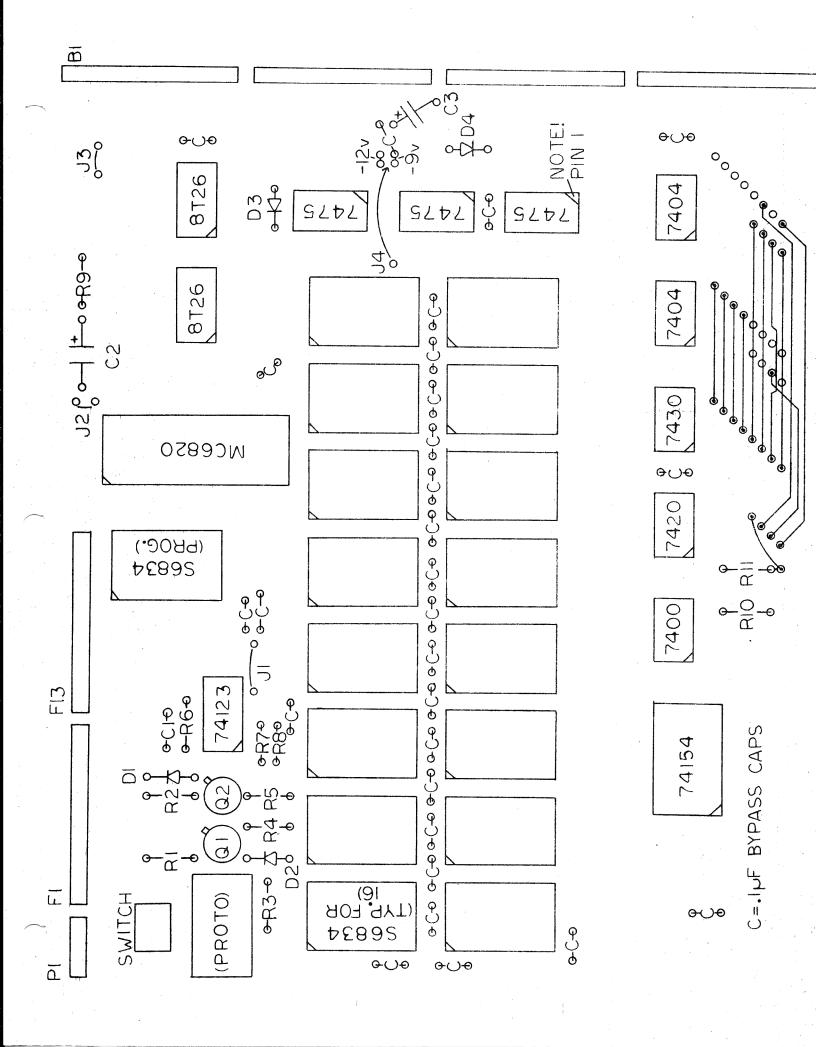

A memory enable signal  $\overline{\text{BEM}}$  derives from  $A_{12}$ - $A_{15}$ . The exact jumper implementation depends on whether the board will contain 4K or 8K of PROM. A 4K board requires decoding all four address lines, which is done by jumpering to the inputs of a 4-input NAND (7420, 1C-K). Jumpering for an even-numbered address (e.g. 6XXX,  $A_{12}$ =0) will result in the eight low order PROM locations on the board being used, while an odd-numbered address (e.g., 7XXX,  $A_{12}$ -1) will cause the eight high-order locations to be used. For 8K implementation  $A_{12}$  is not jumpered to the NAND, rather the unused input is pulled up via R11 (See parts placement diagram). Thus,  $\overline{\text{BEM}}$  will become active for two adjacent 4K memory blocks (e.g., 6XXX and 7XXX) since  $A_{12}$  is not decoded here. In this case,  $A_{9}A_{12}$  are fully decoded to access any one of the 16 PROMS on-board.

$\overline{\text{BEM}}$  and  $\overline{\text{BEP}}$  must be jumpered so that they do not duplicate an address already in use in the system. In particular, they cannot both be set for the same address. If  $\overline{\text{BEP}}$  is set for FØXX, then  $\overline{\text{BEM}}$  cannot be set for FXXX.

Decoding of  $A_9$ - $A_{12}$  is done by a 4-to-16 line decoder (74154, 1C-I). It outputs a low-true condition on one of sixteen lines selected by  $A_9$ - $A_{12}$ . Each line goes to the chip select input (low true) of a different PROM. Inputs G1 and G2 are chip enables (low to enable) which are internally ANDed. If either one goes high all sixteen outputs go high (i.e.,  $A_9$ - $A_{12}$  are ignored). Consequently the PROMs only enable when the board enables ( $\overline{BEM}$  low) and R/W is high (CPU is reading) and  $\emptyset$ 2•VMA is high. Notice that  $\emptyset$ 2•VMA clocks any active output line, in turn clocking the selected PROM.

Low order addresses AgA-g are fed to all PROMs via latches (7475, 1C-F, G, H). Normally, when the board is not in program mode, memory enable (ME) is high and the latches are inoperative. The latch outputs follow the inputs, hence they appear transparent to the PROMs. Latching occurs only in the programming mode, to be discussed below.

A master board enable (BE), derived by NANDing  $\overline{\text{BEP}}$  and  $\overline{\text{BEM}}$ , activates when even either section is addressed. It is used to provide certain control signals. Each time the board is accessed a "wait" signal is generated on B1, stretching  $\emptyset 2$ . This is necessary for the relatively slow S6834's. Also, BE gates system R/W (B40) onto the board via a NAND gate (7420, 1C-KO. R/W determines data direction on the 8T26 data buffers (1C-D, E), and also signals data direction to the CPU via DD (B4). Notice that if the board is not enabled (BE low), the 8T26s are always in the "listen" mode, that is, receiving data from the bus.

## PROM Operation (read only)

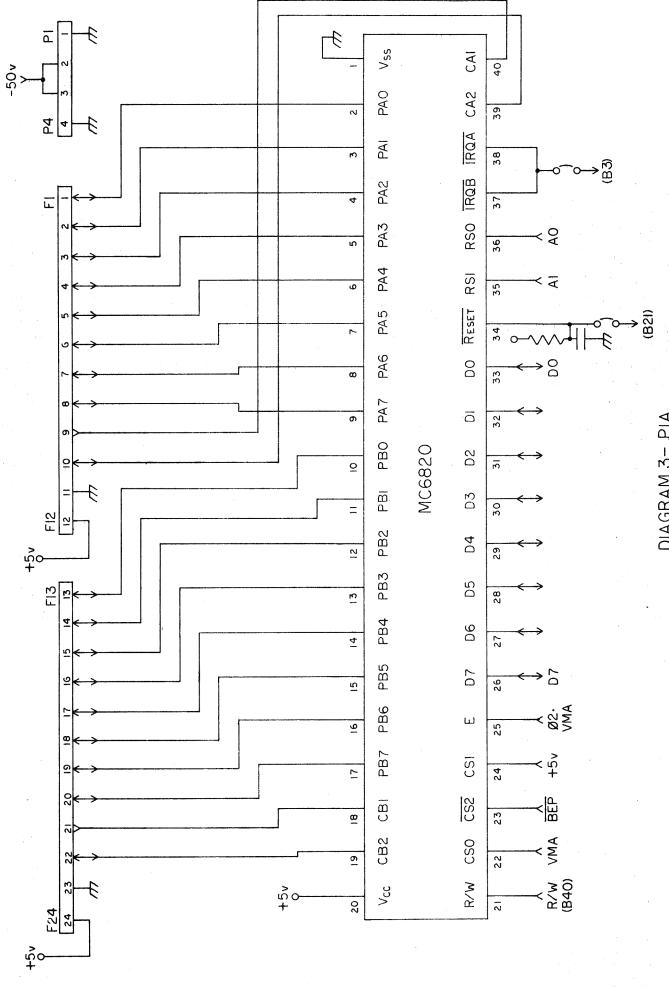

The switch in the upper left corner places the board in normal ("N" position) or program ("P" position) mode. Normal mode places the 8K of PROM on line and disables the programmer. (See Diagram 4). ME (from 1C-J, pin 6) is forced high so  $A_0$ - $A_8$  go directly to the PROMs, i.e., they are not latched. This is the usual board configuration.

For a system Ø2 of 750 KHz or above, wait diode D4 must be installed. Also the Model 400 CPU must be equipped with the two-speed clock option detailed in APP. Note #4A.

## PROM Programmer

The Model 450 PROM Programmer and software allow the user to program and verify an S6834. After erasure, all bits of the PROM are low. Programming is accomplished by setting up an address and data word, pulling the R/W line low, and applying a series of -50V pulses to the Vprog. input. This voltage must be supplied by an off-board power supply (required current is 50ma) which is user-supplied.

For programming, the timing relationships are as follows. The address, data, and  $\overline{\text{CS}}$  must be set up at least 10 usec before the first programming pulse and R/W must go low at least 10 usec before that. The -50V must then be pulsed a specified number of times of specified duration. The amount of programming energy supplies by the -50V pulses must be

# N x $t_{pw} \ge 60$ msec.

to insure program retention, where  $t_{pw}$ =pulse width and N=number of pulses. The maximum pulse width is 5ms, so at least 12 pulses must be applied. Consequently, R/W must hold for a minimum of 66.03 mses, and addresses, data, and  $\overline{\text{CS}}$  must hold for at least 66.02 msec, including

a 10 usec hold time after the end of the last pulse. Some form of latching is required.

Address lines Ag-Ag latch whenever ME line is brought low (Diagrams 2 and 4). With the board in program mode, (switch to the right), thus occurs when the CPU attempts to write into one of the 16 PROMs.  $\overline{\text{BEM}}$  activates allowing  $\emptyset2 \cdot \text{VMA}$  goes high, and will hold that address when  $\overline{\text{BEM}}$  goes high (board deselects) on the next instruction. The address AL $\emptyset$ -AL $\emptyset$  is applied to the PROM to be programmed, and will not change through subsequent programming steps until similarly accessed.

There is no data bus conflict between the 16 PROMs and the programmer because R/W low inhibits the 74154. Thus no other PROM is enabled. Since  $\overline{\text{BEM}}$  does not enable the 16 PROMs in program mode, it is not possible to duplicate directly a PROM in one of these locations. The contents of the PROM must first be transferred into RAM.

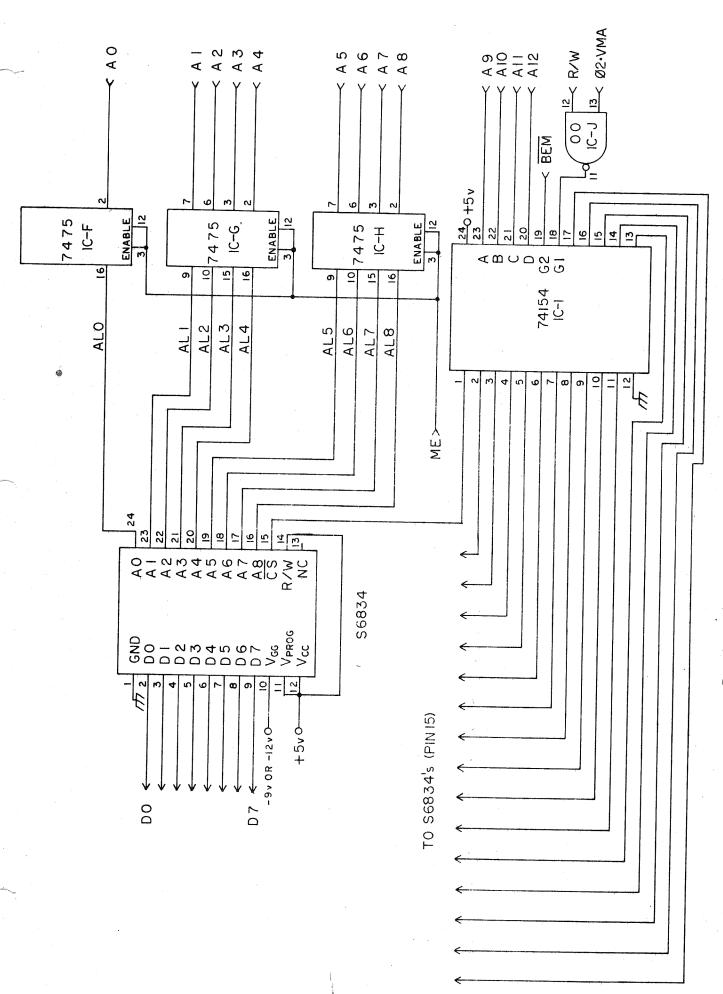

Data is applied to the PROM to be programmed via an MC6820 PIA (Diagram 3), peripheral section "A",. Data stored in the output register will remain "latched" until removed by software. The "B" section of the PIA controls  $\overline{\text{CS}}$  and R/W (PBO & PB1, respectively).

Pulsing of the -50V supply is done by loading a logical "l" into PB2, then loading a logical " $\emptyset$ ". The one-shot (74123, IC-AO triggers on the falling edge applying a high-level pulse to the base of Ql through R3 (100ohm). The width of the pulse is determined by R6 (18K) and Cl (luf), with these values 5 msec.) This turns on Q2, applying a -50V pulse to the Vprog input.

Timing requirements between R/W, address, data and  $\overline{CS}$  lines must be met by software timing. Since the times involved (10 usec) are on the order of 10 clock cycles, this can be done with timing loops. This

method may also be used to determine when a Vprog. pulse has completed (5 msec delay), however, the  $\overline{\mathbb{Q}}$  output of the one-shot can be jumpered to PB4. A polling routine which reads the location and delays execution of the program until the line returns high can then be used.

A programmer driver routine is listed at the end of the manual. When operating, it will display the prompter ")", and expects an input of one of the following four commands (XXX is in hexadecimal form):

- PXXX Programs 512<sub>10</sub> contiguous bytes of RAM into PROM, starting at address XXXX.

- (2) VXXXX Verify. Does a byte-by-byte comparison of PROM with RAM starting at location XXXX for 512 bytes. Normally this should be the same address as used in the program command. The routine outputs a "@" for each unsuccesful comparison.

- (3) RXXXX Reads the contents of the PROM and displays on teletype or CRT. XXXX is a dummy address and can be any value.

- (4) MXXXX Move. Used to duplicate a PROM only. The routine will move the contents of a PROM (in the programming socket) into RAM starting at address XXXX.

The programming procedure section contains specific information on using the routines.

The driver routine as listed is for use with the OSI 65A Monitor and serial terminal. For use with OSI 65V, the user must modify the program. Load OSI's CRT simulator at DE53. Then, change the jump address at location 1060 (assembler line 570) from FEOB to DE53. "INCH". (location 1063, assembler line 580), inputs a character from a keyboard and echoes it. To simulate this under 65V load the following program starting at location 11DA:

11DA 20 ED FE 20 53  $\phi$ E 60 Then, change the JMP address at 1063 from FE00 to 11DA.

### PIA PORT

The 450 board contains an OSI standard PIA port (Diagram 3). The output lines run to two Molex connectors at the top left of the board. +5V power and GND are also brought out at several places on the connectors.

R9-C2 form an automatic power-on reset circuit. In lieu of this, B21 may be dedicated as a system reset. An off-board power-on reset circuit must then be implemented, and jumper J2 installed.

If interrupt operation is desired, install J3 to system  $\overline{\text{IRQ}}$ . The user must supply software servicing routines.

### Parts List

```

PROM only

Model 450 Board

1

V2

8T26

/1

7400~

2 7404

\sqrt{1}

7420~

1

7430 ~

7475 ~

74154

∕2 1K 1/4 watt (R10, R11) ∕

2 IN914 (D3, D4)

.luf bypass caps√

1 25uf 24V electrolytic (C3)√

1 to 16 S6834 PROMs

Programmer

74123 🗸

4

MC6820 PIA

100ohm (R3)

220 ohm (R5)

1K (R7)~

4.7K (R1, R2, R8, R9)

18K (R6)

22K (R4)

· 1

1.0 uf mylar (Cl)

1

25uf 25V electrolytic (C2)

IN4001 diode (D1, D2)

CGE 71

PNP transistors 2N398B or equiv. (Q1, Q2)

3 T

DPDT slide switch >

24-pin socket (ZIF preffered)

4 pin Molex (KK-156) Power connections

Optional

PROM Sockets as Desired

```

```

4 Molex KK-156 Connectors (B1-B48)

2 Molex KK-156 Connectors (F1-F24) (PIA PORT only)

```

#### CONSTRUCTION:

- Step 1: Carefully inspect for foil shorts and breaks. Back-light the board and, using a magnifying glass, inspect the back of the board. Pay particular attention to the foil runs between pins on the PROMs. If there are any shorts they will probably occur here. Cut shorts with a sharp razor or Exacto knife.

- Step 2: Install as many PROM sockets as desired. Install a socket at the programming location [marked (Prog) on overlay]. Install all TTL parts, 8T26s, and PIA. Notice that the 7475s are installed with pin 1 toward the bottom of the board.

- Step 3: Install resistors R1-R11. Refer to parts list for values, and overlay for locations. Similarly install capacitors C1-C3. (Note: R9-C2 provide automatic power-on reset of the PIA. B21 may be dedicated as a system reset line, in which case, omit R9-C2 and install J2. External reset must then be provided to B21.) Install the switch.

- Step 4: Install jumper J4. Jl and J3 are optional.

- Step 5: Install D1-D4, observing the correct polarity. Install Q1, Q2.

- Step 6: Install all bypass capacitors (marked "C" on the over-lay).

- Step 7: (Address Jumpering) The board must normally be jumpered to enable the PROMs on AXXX, the programmer on FØXX. Jumper as shown on the overlay (lower right corner).

- Step 8: Install four Molex connectors along the right edge of the board (B1-B48). Install the power connector (4 pin Molex) at Pl (top left corner of the board). If using the PIA port, install two male Molex connectors at Fl-Fl2.

- Step 9: Verify that the memory space of the Model 450 is unused by any other board in the system. Install the board on backplane or Model 498 Card Extender to backplane. Verify programmer operation by programming a PROM according to the procedure outlines at the end of this section. CAUTION: NEVER install or remove a PROM from the programming socket with the switch in "Program" position. Doing so may result in destruction of the PROM. The PROM may be removed with the switch in "normal" position.

- Step 10: Install the PROMs programmed in Step 9. The location marked "S6834 (Typ. for 16)" on the overlay is the lowest-order PROM. Next fill the bottom position in this column, then the top position next column, etc. CAUTION: PROMs should never be removed from these sockets with the system power on!

## Programming Procedure:

- (1) With system power turned off, connect Model 498 Card Extender to backplane. Connect Model 450 PROM Board to Extender.

- (2) Turn system power on.

- (3) Load in programmer driver routines. If using a video-based system, modify as described in theory of operation. On either system, load locations 0129, 012A, 012B, 012C with 00. Load 012D with 28.

- (4) To duplicate a PROM, disconnect -50V supply and place mode switch to the right (program). Execute the driver routine (starting address is 1000 hex). The routine will output the prompter ")". Enter MXXXX/to move the contents of PROM into RAM starting at address XXXX. Be careful not to over-write the driver routine! Return switch to normal position, and remove the PROM.

- (5) Make sure the Mode switch is in the normal position. Connect -50V supply via the 4-pin Molex connector at the top left corner of the board.

- (6) With mode switch in normal position, insert a blank PROM into the programming socket. Set mode switch to "Program" position. Enter PXXX, where XXXX is the starting address of the block of RAM to be programmed into PROM. For Ø2 of 1 MHz, programming requires two minutes. (Note: the driver routines can be used with clock speeds up to 2 MHz.) When programming is complete, the driver will output the prompter. Verify correct programming by entering VXXXX, where XXXX is the same starting address as

used to program the PROM. If all is well, the prompter will return. Otherwise a "@" will output, once for each faulty byte. If this occurs, return to the beginning of Step 6 and reprogram. (This is recommended even if all bytes check out. Programming twice helps ensure data retention.) Return mode switch to normal position, and remove the PROM.

(7) If another PROM is to be programmed, return to Step 4 (to duplicate) or Step 5.

All S6834 PROMs are shipped from the factory with all bits high, and so must be erased prior to programming. A GE germicidal lamp is a suitable source. It can be used in any fluorescent fixture. Place the quartz window of the PROM 4 inches from the lamp for 15 minutes.

CAUTION: The UV light produced by this lamp can damage eyesight!

NEVER look directly into the lamp!

DIAGRAM 1- ADDRESS DECODING

DIAGRAM 2- PROM IMPLEMENTATION

DIAGRAM 3- PIA

DIAGRAM 4- PROM PROGRAMMER

```

10 0000 ; OSI 450 PROM PRORAMMER

20 0000 ; DRIVER ROUTINES. (CT>2MHZ)

30 0000 WHRL =$0

40 0000 WHRH=$1

40 0000 WHRH=$1

50 0000 SAML=$2

60 0000 SAMH=$3

70 0000 CNT=$4

80 0000 MODE=$5 O=>READ, ELSE COMPARE

90 0000 FLAG=$6 O=>READ, ELSE MOVE

100 0000 FLIPF=$7

110 0000 WHERE=$10

120 1000 *=$1000

130 1000

140 1000 A228 PCNTP IDV #500

570 1060 4COBFE OUTCH JMP $FEOB 580 1063 4COOFE INCH JMP $FEOO

590 1066

```

```

600 1066 A201 BUILD LDX #1 READ ADDRESS

610 1068 206010

JSR BYTE

620 106B CA

DEX

630 106C 207D10 BYTE JSR IND

640 106F 0A

ASL A

ASL A

ASL A

ASL A

STA WHRL, X

JSR IND

ORA WHRL, X

STA WHRL, X

ASL A

650 1070 OA

660 1071 OA

670 1072 OA

680 1073 9500

690 1075 207D10

700 1078 1500

710 107A 9500

720 107C 60

RTS

730 107D

740 107D 206310 IND JSR INCH

750 1080 C930 CMP #'0

760 1082 30D4 BMI ILLI

770 1084 C93A CMP #':

780 1086 300B BMI OK1

790 1088 C941 CMP #'A

BMI ILLEG

800 108A 30CC

BMI ILLEG

810 108C C947

CMP # G

820 108E 10C8

BPL ILLEG

830 1090 18

CLC

840 1091 E906

SBC #6

0K1

850 1093 290F

AND #SF

860 1095 60

RTS

870 1096

COMPARE DATA

950 10A4 8A

TXA

960 10A5 F004 BEQ INT

970 10A7 A2FF MOVE LDX #$FF

MOVE DATA

980 10A9 A900 LDH #0

990 10AB 8606 INT STX FLAG

1000 10AD 8505 INTO STA MODE

1010 10AF A000 LDY #0 INIT PIA

1020 10B1 8C01F0 STY $F001

1030 10B4 8C00F0 STY $F000

1040 10B7 A204 LDX #4

1050 10B9 8E01F0 STX $F001

1060 10BC 8C03F0 STY $F003

1070 10BF 88 DEY

980 10A9 A900

LDA #0

STX $F001

STY $F003

DEY

1070 10BF 88 DEY

1080 10C0 8C02F0 STY $F002

1090 10C3 8E03F0 STX $F003

1100 10C6 C8 INY

1110 10C7 A505 LDA MODE

1120 10C9 D004 BNE INO

1130 10CB A506 LDA FLAG

1140 10CD F006 BEQ OTHR

1150 10CF 8402 INO STY SAML

1160 10D1 A9A0 LDA #$A0

LDA #$!

STA SA!

OTHR LDA #8

1160 10D1 A9A0

LDA #$AO

1170 10D3 8503

STA SAMH

1180 10D5 A908

1200 10D9 201D11 1210 10DG 201

JSR CHLF

1210 10DC 204400 ADR JSR OBTAN-BLAST+WHERE

1220 10DF E406 CPX FLAG

1230 10E1 B005

BCS ROP

1240 10E3 9100

STA (WHRL).Y

```

```

1250 1055 400511

1260 1056 48

1270 1059 A90F

1280 1056 8002F0

1290 1056 48

1300 1056 48

1300 1056 48

1300 1056 48

1310 1070 4A

1280 1071 4A

1330 1072 4A

1340 1073 4A

1340 1073 4A

1350 1074 202711

1360 1077 68

1370 1078 202711

1360 1076 202711

1360 1077 68

1370 1078 202711

1360 1078 202711

1360 1077 68

1370 1078 202711

1360 1077 808

1390 1079 206010

1400 1100 604

1410 1100 2000

1420 1104 201011

1430 1107 A908

1440 1100 8002F0

1470 1110 C8

1440 1100 8002F0

1470 1110 C8

1480 1111 1009

1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 28

1500 1117 290F

1600 1127 57

1610 1127 290F

1600 1128 290P

1600 1134 2601P

1700 1134 8600PO

1730 1140 8600PO

1730

```

```

1870 1160 201000

1880 1163 A914

1890 1165 A504

1900 1167 A507

1910 1169 D006

1920 1168 A901

1930 1168 A901

1930 1171 C8

1960 1172 D024

1970 1174 E601

1980 1176 E603

1990 1176 E603

2010 1176 E003

2010 1176 E003

2010 1176 E003

2010 1176 E003

2010 1176 E004

2020 1176 E0

2030 1177

2040 1168 A90C

2030 1188 B005F0

2120 1189 B100

2110 1189 B005F0

2120 1189 B005F0

2130 1191 A908

2140 1193 A802F0

2150 1196 A90C

2150 1198 A90C

2100 1198 B00F0

2101 1198

```

```

2450 11CA 206010

JSK OUTCH

2460 11CD 68

NEXTE PLA

2470 11CE 68

PLA

2480 11CF 4C0B11

JMP NEXT

2490 11D2 AD00F0

RDR

LDA $F000

ENDR

RTS

2500 11D5 60

. END

2510 11D6

```

#### SA

#181018AD80118503AE8111B1029100C8CAD0F8206310482066106809BD ;181030C956D0062096104C0010C950D0062034114C0010C94DD006080B ;18104820A7104C0010C952D006209A104C0010A93F2060104C0010068E ;1810604C0BFE4C00FEA201206C10CA207D100A0A0A0A9500207D100747 ;1810781500950060206310C93030D4C93A300BC94130CCC94710C80966 :18109018E906290F60A9FF3013A200A5008502A50185038AF004A2095E ;1810A8FFA90086068505A0008C01F08C00F0A2048E01F08C03F0880B53 ;1810C08C02F08E03F0C8A505D004A506F0068402A9A08503A908850B5B ;1810D804201D11204400E406B00591004C0B1148A90F8D02F06848077D \$1810F04A4A4A4A20271168202711A920206010C604D00C201D11A9074E :181108088504A90F8D02F0C8D0C9E601E603E8E006D0C060A90D200BBE \$1811206010A90A4C6010290F0930C93A900269064C6010A0008C010686 ;181138F08C03F0888C00F08C02F0A2048E01F08E03F0C8840284070BD1 ;181150A9A08503A9148504A90D8D02F020B111201000A9148504A508C2 ;18116807D006A9018507D0E7C8D0E4E601E603A9A2C503D0DA60820D46 **;1811801154B102A90C8D02F0B1008D00F0203F00A9088D02F0A90C0967** ;1811988D02F038A910A280CAD0FDE901B0F7C604D0E6A90F8D02F00E32 ;1811B060EAEAEAEA60B102A90E8D02F0A505F011AD00F0D100F0050D38 :0E11C8A94020601068684C0B11AD00F0600595